# Kapitel 1

# Einleitung

Vor 60 Jahren, im Juni 1948, wurde von den *Bell Labs* der erste Transistor öffentlich demonstriert. Weniger bekannt, aber ebenso wichtig ist die Demonstration des ersten Metal-Oxide-Semiconductor (MOS) Transistors; damit wurde im Jahre 1960 der Grundstein für die moderne Informationsgesellschaft gelegt [Loj07]. Ohne diese Entdeckungen bzw. Erfindungen würde es heute die vielen elektronische Geräte, wie Taschenrechner, Personal Computer, Mobiltelefone, Internetserver, Laptops, MP3-Player und Multimediageräte, um nur einige der unzählbaren Beispiele zu nennen, in dieser Form nicht geben. Diese rasante Entwicklung der Informations-, Kommunikations- und Unterhaltungstechnologien folgt, angetrieben durch wirtschaftliche Interessen, dem Mooreschen Gesetz.

Das *Mooresche Gesetz* besagt, dass sich durch den technischen Fortschritt die Komplexität von integrierten Schaltkreisen etwa alle 18 bis 24 Monate verdoppelt. Bereits 1965 schrieb Gordon Moore in einem Artikel der Zeitschrift "Electronics Magazine", dass die Dichte der Transistoren auf einer integrierten Schaltung mit der Zeit exponentiell ansteigt und sich jährlich verdoppelt [Moo65]. Erst später wurde eine detailliertere Prognose postuliert, in der G. Moore den zukünftigen Komplexitätszuwachs auch leicht nach unten korrigierte [Moo75]. Ebenso wurde beschrieben, wie der Zuwachs erreicht werden kann: Die größte Bedeutung wurde damals wie heute dem so genannten *Scaling*, also der Verkleinerung der Fläche eines Transistors, zugeschrieben.

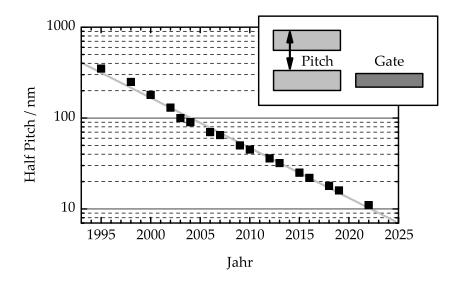

Ob es sich beim Mooreschen Gesetz um eine geniale Prognose oder um eine sich selbst erfüllende Prophezeiung handelt spielt keine Rolle<sup>1</sup>, das Mooresche Gesetz ist zur Zielvorgabe der Halbleiterindustrie geworden: Dieser Fahrplan wird jedes Jahr in der *International Roadmap for Semiconductors* (ITRS)<sup>2</sup> von einem internationalen Expertengremium aktualisiert und spezifiziert. Abbildung 1.1 zeigt am Beispiel der DRAM-Dichte wie sich die exponentielle Mi-

<sup>&</sup>lt;sup>1</sup>Der Name Mooresches Gesetz ist durchaus irreführend, da es sich nicht um ein Gesetz handelt.

<sup>&</sup>lt;sup>2</sup>http://www.itrs.net/

2 1. EINLEITUNG

niaturisierung in den letzten Jahren bewahrheitet hat und wo die Prognose bzw. die Ziele der nächsten Jahre liegen.

Das Scaling wird jedoch immer aufwändiger und es wird in der Zukunft an seine physikalischen Grenzen stoßen, da eine Vielzahl von unerwünschten Effekten (z.B. Kurzkanaleffekte, quantenmechanische Effekte) die Eigenschaften der einzelnen Transistoren auf dem Chip beeinträchtigen [ITR07]:

Scaling planar bulk CMOS will face significant challenges due to the high channel doping required, band-to-band tunneling across the junction and gate-induced drain leakage (GIDL), random doping variations, and difficulty in adequately controlling short channel effects.<sup>3</sup>

Um den Fortschritt und das Wirtschaftswachstum der Halbleiterindustrie und damit auch der Elektronikindustrie zu sichern, werden Lösungen für ein kontinuierliches Scaling gesucht. Neben der Optimierung heutiger Transistoren (MOS-Feldeffekt-Transistoren, MOSFET) wird auch nach Alternativen zu diesem Bauelement gesucht.

**Abbildung 1.1:** Entwicklungstendenz in der Halbleiterindustrie anhand des DRAM [ITR07]. Mit "Half Pitch" wird die Hälfte der kleinst möglichen Wiederholung von Strukturen bezeichnet. Nach diesem Wert wird häufig auch der jeweilige Technologieknoten bezeichnet (z. B. 65 nm-Technologie). Die minimale Gatelänge ist noch kleiner.

Der *Tunnel-Feldeffekt-Transistor* (TFET) ist ein neuartiges Bauelement, welches den MOSFET in Zukunft ersetzten könnte. Das Grundprinzip beruht auf

<sup>&</sup>lt;sup>3</sup>Details hierzu werden in Kapitel 2 behandelt.

der Steuerung von quantenmechanischem Tunneln, das beim MOSFET gänzlich unerwünscht ist. Aufgrund der unterschiedlichen Arbeitsweise kann der TFET deutlich stärker verkleinert werden als ein MOSFET und birgt daher großes Potential für zukünftige integrierte Schaltungen auf Halbleiterchips.

#### Ziel und Aufbau der Arbeit

Das Ziel dieser Arbeit ist die *experimentelle Untersuchung* des Tunnel-Feldeffekt-Transistors, sowie die Charakterisierung und Optimierung von TFETs mit ultra-kurzen Kanallängen. Um einen MOSFET-Nachfolger zu bewerten, ist es notwendig die Funktionsweise, die Eigenschaften und die Grenzen heutiger Bauelemente zu kennen. Diese Punkte werden in Kapitel 2 behandelt. Kapitel 3 stellt den Tunnel-Feldeffekt-Transistor vor: Dies beinhaltet die Erklärung der physikalischen Funktionsweise, die Optimierungsmöglichkeiten, den Vergleich mit dem MOSFET und ein Überblick über bisherige Arbeiten zum TFET.

Die technologische Durchführung dieser Arbeit wird in Kapitel 4 beschrieben. Für die Realisierung von TFETs mit kurzen Kanallängen wurde die so genannte Spacer-Gate-Technologie eingesetzt. Diese neue Herstellungsmethode wird erklärt und das notwendige Zusammenspiel zwischen den Einzelprozessen mit der gesamten Herstellung wird erläutert. Die Ergebnisse der elektrischen Charakterisierung der Spacer-Gate-TFETs werden in Kapitel 5 vorgestellt und diskutiert. Eine allgemeinere Bewertung der Spacer-Gate-Technologie wird in Kapitel 6 vorgenommen. Abschließend zeigt dieses Kapitel Ideen für zukünftige Forschungsarbeiten und gibt einen Ausblick auf mögliche Einsatzgebiete des Tunnel-Feldeffekt-Transistors.

# Kapitel 2

## Funktionsweise des MOSFET

In der CMOS-Technologie ist der Metal-Oxide-Semiconductor Field-Effect-Transistor (MOSFET) das wichtigste Bauelement. In diesem Kapitel wird die Arbeitsweise eines MOSFET vorgestellt. Abschnitt 2.1 erläutert das physikalische Grundprinzip eines so genannten Langkanal-MOSFET und dessen Eigenschaften bezüglich der Skalierbarkeit.

Abschnitt 2.2 behandelt den MOSFET, wenn die Schwelle vom langen zum kurzen Kanal überschritten wird. Dadurch treten Kurzkanaleffekte auf, welche die elektrischen Eigenschaften verschlechtern und den Entwurf von integrierten Schaltungen aufwändiger gestalten bzw. unmöglich machen. Probleme und mögliche Lösungsansätze werden vorgestellt.

### 2.1 Langkanal

Ein MOSFET besteht im Wesentlichen aus einer Metal-Oxide-Semiconductor (MOS)-Diode, welche zwischen zwei Kontakten liegt und dadurch den Stromfluss zwischen diesen beiden Kontakten steuert. Der besseren Verständlichkeit halber wird hier nur der selbst sperrende *n*-MOSFET beschrieben, alle Erläuterungen können aber leicht auf den dazu komplementären *p*-MOSFET übertragen werden.

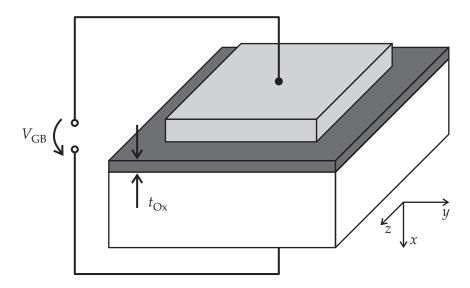

### 2.1.1 MOS-Diode

In Abbildung 2.1 ist der schematische Aufbau einer MOS-Diode zu sehen. Zwischen dem Metall und dem Halbleiter kann idealerweise kein Gleichstrom fließen, es besteht aber eine kapazitive Kopplung zwischen Metall und Halbleiter. Die Kapazität des Gesamtsystems ist abhängig von der Geometrie, den verwendeten Materialien und von der angelegten Spannung. Die angelegte Spannung bestimmt auch die Ladungsverteilung innerhalb der Raumladungszone des Halbleiters.

**Abbildung 2.1:** Schemazeichnung einer MOS Diode mit Koordinatensystem,  $t_{Ox}$  ist die Dicke des Gateoxids.

Unter Betriebsbedingungen eines MOSFET befindet sich der Halbleiter unter dem Gateoxid je nach Gate-Bulk-Spannung  $V_{\rm GB}$  entweder in

- Verarmung

- schwacher Inversion oder

- starker Inversion.

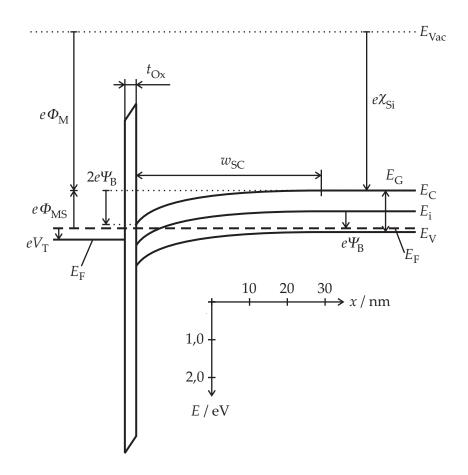

Der Übergang von schwacher zu starker Inversion liegt per Definition vor, wenn die Bandverbiegung des Halbleiters  $2\Psi_B$  beträgt, wobei  $\Psi_B$  der energetische Abstand des Fermi-Niveaus  $E_F$  vom intrinsischen Fermi-Niveau  $E_i$  im Halbleiter ist und durch die Dotierung im Halbleiter festgelegt wird [Mue91]. Abbildung 2.2 zeigt für diesen Fall das maßstabsgetreue Bänderdiagramm einer MOS-Diode auf p-Silizium. Das Valenzband  $E_V$ , das Leitungsband  $E_C$  und die intrinsische Fermi-Energie im Halbleiter werden durch die Gate-Bulk-Spannung  $V_{GB}$  und die Austrittsarbeitsdifferenz  $\Phi_{MS}$  im Bereich der Raumladungszone  $w_{SC}$  beeinflusst. In [Nic82] werden die Details der MOS-Diode ausführlich beschrieben.

Die Spannung  $V_{GB}$ , bei der die Bandverbiegung  $2\Psi_B$  vorliegt, wird Einsatzspannung  $V_T$  genannt. Sie lässt sich berechnen durch

$$V_{\rm T} = V_{\rm FB} + 2\Psi_{\rm B} - \frac{Q_{\rm S}}{C_{\rm Ox}}$$

(2.1)

wobei  $V_{\rm FB}$  die Flachbandspannung,  $Q_{\rm S}$  die Ladung in der Raumladungszone und  $C_{\rm Ox}$  die Oxidkapazität ist . Die Höhe von  $V_{\rm FB}$  hängt von der Austrittsarbeit

2.1. Langkanal 7

**Abbildung 2.2:** Maßstabstreues Bänderdiagramm einer MOS-Diode mit anliegender Einsatzspannung  $V_{\rm GB}=V_{\rm T}$ . Substrat: p-dotiertes Silizium  $N_{\rm A}=5{\rm E}17/{\rm cm}^3$ , Gatedielektrikum: 3 nm SiO<sub>2</sub>, Gatematerial: entartetes n-Polysilizium.

des Gatematerials  $\Phi_{\rm M}$ , der Dotierung des Halbleiters, Ladungen im Oxid und Grenzflächenzuständen ab. Steigt  $V_{\rm GB}$  über  $V_{\rm T}$ , so erhöht sich die Anzahl der Inversionsladungsträger an der Siliziumgrenzfläche exponentiell [Mue91]. Die Einsatzspannung ist eine wichtige charakteristische Größe des MOSFET, da ab dieser Schwelle das Bauelement eingeschaltet wird, also ein Strom von Source nach Drain fließt.

### 2.1.2 *n*-MOSFET

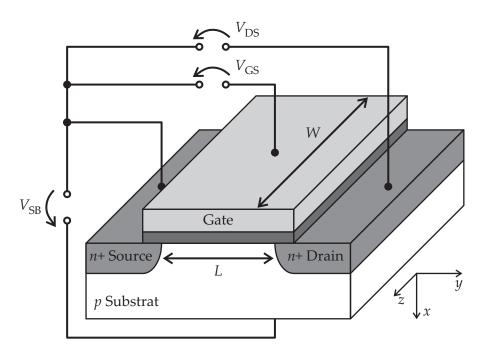

Abbildung 2.3 zeigt den schematischen Aufbau eines MOSFET mit den vier Anschlüssen: Source, Drain, Gate und Bulk. *L* und *W* bezeichnen die Kanallänge und -weite. Die Gateelektrode ist durch das dünne Gateoxid vom *p*-dotierten Siliziumsubstrat (Bulk) elektrisch isoliert. Die Source- und Draingebiete sind *n*-dotiert und bilden zusammen mit dem Substrat zwei *pn*-Dioden.

**Abbildung 2.3:** Schemazeichnung eines *n*-Kanal MOSFET mit den zugehörigen Betriebsspannungen und ausgewählten Geometrieparametern.

Das Kanalgebiet unter dem Gate ist üblicherweise für die Einstellung der Einsatzspannung etwas höher p-dotiert als das Substrat, es bildet aber mit Source und Drain ebenfalls zwei Dioden. Generell gilt, dass der MOSFET ein symmetrisches Bauelement bezüglich der Kontakte Source und Drain ist. Erst durch die äußere Beschaltung wird die unterschiedliche Bezeichnung sinnvoll. Beim n-MOSFET sind die Spannungen  $V_{\rm DS}$  und  $V_{\rm GS}$  größer als 0 V, so dass die Source auch als Quelle der Elektronen und Drain als Senke der Elektronen bezeichnet wird. Betrachtet man den Bereich von Source nach Drain so stellt man fest, dass unabhängig von der äußeren Beschaltung eine dieser beiden Dioden immer in Sperrrichtung gepolt ist. Über das Substrat kann also kein Strom von Source nach Drain fließen.

Im ausgeschalteten Zustand ( $V_{\rm GS} \ll V_{\rm T}$ ) befindet sich der Halbleiter unter dem Gate, das so genannte Kanalgebiet, in Verarmung (vgl. Abschnitt 2.1.1). Die Anzahl der freien Ladungsträger, die zum Stromtransport beitragen könnten ist also vernachlässigbar klein und der Transistor sperrt.

Bei einer Spannung  $V_{\rm GS}$  oberhalb von  $V_{\rm T}$  liegt im Kanalgebiet starke Inversion vor. Die Anzahl der Minoritätsladungsträger unter dem Gate ist um einige Größenordnungen höher und der so gebildete Elektronenkanal ermöglicht den Stromfluss von Source nach Drain: Der Transistor ist leitend.