# **Einleitung**

Die von Gordon Moore 1965 veröffentlichte Annahme, dass sich die Komplexität integrierter Schaltungen alle 18 Monate verdoppelt [1], erwies sich als wegweisend für die Entwicklung der Halbleitertechnologie. Diese als "Moore's Law" bekannte Annahme entwickelte sich zum Taktgeber für die gesamte Elektronikbranche [2]. Basierend auf Moore's Law wird über die International Technology Roadmap for Semiconductors (ITRS) die Entwicklung in der Halbleiterindustrie gesteuert [3].

Seit etwa 2000 werden immer wieder fundamentale Grenzen erreicht, die durch Entwicklungen in der Prozesstechnologie umgangen werden müssen. Dem mit abnehmender Größe zunehmenden Einfluss ungewollter physikalischer Effekte wird durch den Einsatz neuer Materialien und Modifikationen des klassischen MOSFET-Konzepts begegnet [2]. Materialbezogen werden zwei Möglichkeiten zur Verbesserung der Transistoreigenschaften verfolgt:

Um bei abnehmender Strukturgröße die Gatekapazität konstant zu halten, muss die Dicke des Gatedielektrikums verringert werden. Mit abnehmender Dicke des Gateoxides steigen aber die Leckströme an und die Verlustleistung erhöht sich. Dem kann durch Ersetzen des Siliziumoxids durch ein Material mit höherer Dielektrizitätskonstante (high-k,  $\varepsilon_r > 3.9$ ) entgegen gewirkt werden, da zum Erreichen der gleichen Kapazität pro Fläche eine höhere physikalische Schichtdicke erforderlich ist. Diese Lösung hat sich im industriellen Einsatz bewährt [4].

Zur Erhöhung der Stromdichte hat sich verspanntes Silizium-Germanium (strained SiGe) zur Verbesserung der Ladungsträgerbeweglichkeit im Kanal der MOSFETs Anfang des Jahrzehnts durchgesetzt und wird mittlerweile von Intel in der fünften Generation weiterentwickelt [5].

Mit der Skalierung geht ebenfalls eine Reduzierung der Einsatzspannung einher. Die minimale Einsatzspannung ist begrenzt durch die Forderung des Verhältnisses von Leckstrom zu Strom im eingeschalteten Zustand von fünf Dekaden. Das physikalische Limit für die sogenannte Unterschwellsteigung (Subthreshold Slope), ein Maß für den Stromanstieg bei steigender Spannung, beträgt beim konventionellen MOSFET 60mV pro Dekade. Üblich sind heute 100mV pro Dekade. Die minimale Versorgungsspannung beträgt damit 1V, was nicht den Anforderungen der ITRS entspricht, die für 2013 bei  $V_{\rm DD}{=}0.85V$  (Einsatzspannung  $V_{\rm T,Sat}=0.3V$ ) liegen [3]. Da die Begrenzung der Unterschwellsteigung auf dem Ladungsträgertransport durch Diffusion beruht, handelt es sich um ein fundamentales physikalisches Limit [6]. Somit stößt das konventionelle MOSFET-Konzept an seine Grenzen.

Es existieren bereits Transistorkonzepte, die das klassische MOSFET-Konzept ersetzen können, sollte es nicht mehr möglich sein, die technologischen Grenzen näher an die physikalischen Grenzen zu verschieben. Bisher erwies es sich durch die einfachere Prozessführung als lohnender, durch Weiterentwicklung bestehender Technologien die physikalischen Probleme zu umgehen, so dass sich alternative Konzepte nicht durchsetzen konnten.

Mit dem erneuten Erreichen physikalischer Grenzen, erkennbar am verstärkten Einfluss der oben genannten Effekte, gewinnen alternative Konzepte in letzter Zeit an Attraktivität. Nichtplanare Multigate-Konzepte wie Fin-FET oder der 2002 entwickelte TriGate-Transistor werden seit 2012 in Speicherchips und Prozessoren eingesetzt [5, 7]. Damit kann die Gültigkeit von Moore's Law vorerst erhalten werden. Diese Konzepte basieren immer noch auf dem planaren MOSFET, der Kanal bildet sich parallel zur Waferoberfläche aus. Eine Verbesserung der Parameter wird durch eine erhöhte Gatesteuerwirkung erreicht. Nicht alle unerwünschten physikalischen Effekte lassen sich so umgehen. Es ist eine Frage der Zeit, bis das planare MOSFET-Konzept gänzlich ausgedient hat.

Durch die Öffnung für die dritte Dimension sind alternative vertikale Konzepte, deren Kanal senkrecht zur Substratoberfläche ausgebildet wird und deren Stromtransport auf anderen Mechanismen als denen des klassischen MOSFETs beruht, verstärkt von Interesse. Beispielhaft seien hier der vertikale Tunnel-Feldeffekttransistor (TFET) [8] und der vertikale Stoßionisationstransistor (Impact Ionsation MOSFET, IMOS) [9] genannt. Während der Stromtransport im MOSFET durch Diffusion begrenzt ist, erfolgt der Transport im TFET über einen Tunnelstrom und im IMOS durch Stoßionisation. Dies resultiert unter anderem in einem sehr schnellen Einschaltverhalten durch eine Unterschwellsteigung jenseits des physikalischen Limits für MOSFETs (Steep Subthreshold Slope Device), so dass eine Reduzierung der Versorgungsspannung möglich ist, ohne die Leckströme signifikant zu erhöhen [9, 10, 11]. Da der IMOS im Gegensatz zum TFET Ströme liefern kann, die innerhalb der Vorgaben der ITRS liegen, liegt der Fokus der Untersuchungen auf diesem Konzept.

Die Kanallänge der vertikalen Transistoren ist nicht mehr durch Lithografie definiert, sondern durch die Dicke epitaktisch gewachsener Schichtstapel. Beide Konzepte beinhalten sogenannte Delta-Schichten, extrem hochdotierte Schichten, deren Dicke nur wenige Nanometer beträgt. Durch die Konzentration der Dotierung auf eine dünne Schicht sind sehr kurze Kanallängen möglich.

Zur epitaktischen Abscheidung von Siliziumschichten im industriellen Maßstab kommt die chemische Gasphasenepitaxie (Chemical Vapor Deposition, CVD) zum Einsatz. Dem Vorteil höherer Wachstumsgeschwindigkeit, geringerer Defektdichte und der Möglichkeit der Batchprozessierung stehen hohe Prozesstemperaturen und hohe Anforderungen an die Sicherheitstechnik gegenüber [12].

Das hohe Temperaturbudget erschwert die Anwendung der CVD bei der Herstellung von Bauteilen, die Delta-Schichten enthalten. Bei den hohen erforderlichen Temperaturen

viii

mindert Diffusion die scharfe Begrenzung des dotierten Bereiches. Um gute elektrische Eigenschaften zu erhalten, müssen die Schichten möglichst scharf begrenzt bleiben. Eine Alternative bietet hier die Molekularstrahlepitaxie (Molecular Beam Epitaxy, MBE), ein Verfahren zur physikalischen Abscheidung von Schichten. Geringere Prozesstemperaturen stehen hier sehr hohen Anforderungen an Reinheit und Vakuum in der Prozesskammer gegenüber. Mit der Verbreitung von Ultahochvakuumsystemen in der 1970er Jahren begann die systematische Entwicklung von abrupten Dotierprofilen [13]. Seit Ende der 1980er Jahre ist diese Technologie ausgereift, so dass die vertikale Anordnung unterschiedlich dotierter Schichten mit scharfen Übergängen zwischen dotierten Bereichen in kristallinem Silizium möglich ist [14]. Aufgrund der langen Prozesszeit und hohen Anforderungen an die Produktionsanlagen und damit hohen Kosten hat sich die Molekularstrahlepitaxie vor allem in der Abscheidung von III-V-Heterostrukturen durchgesetzt und stellt in der Siliziumtechnologie eher eine Ausnahme für Prozesse mit besonderen Anforderungen, wie die Erzeugung von Delta-Schichten, dar.

Zusätzlich zur Epitaxie tragen noch die Erzeugung des Gatestacks und die Abscheidung der Passivierung entscheidend zum Temperaturbudget bei [15]. Im Rahmen dieser Arbeit wird daher untersucht, inwiefern sich das gesamte Temperaturbudget des Prozesses für den vertikalen IMOS senken lässt. Der naheliegende Ansatz ist die Integration der oben genannten Materialverbesserungen in das bereits erfolgreich in konventioneller Siliziumtechnologie demonstrierte Konzept [16]. Ausgehend von oben angewandtem Prozess wird dieser unter Erhaltung der CMOS-Kompatibilität zu einem Niedertemperaturprozess weiter entwickelt. High-k Materialien aus einem Atomic Layer Deposition (ALD) Prozess, hier wird Aluminiumoxid eingesetzt, bieten eine substratunabhängige Möglichkeit, qualitativ hochwertige Dielektrika bei niedrigen Temperaturen abzuscheiden. Die Entwicklung eines Metal-Gates und einer Niedertemperaturpassivierung stellen sicher, dass die Temperatur im gesamten Prozess so niedrig bleibt, dass keinerlei Diffusionsprozesse der Dotierstoffe stattfinden. Zusätzlich ermöglicht der entwickelte Prozess die Integration verspannter Silizium-Germanium-Schichten in den funktionalen Schichtstapel. Das Wachstum dieser verspannten Schichten erfolgt bei deutlich geringeren Temperaturen als reines Siliziumwachstum. Eine Relaxation ist bei dem in dieser Arbeit entwickelten Prozess ausgeschlossen.

Es wird gezeigt, dass die Integration von higk-k Dielektrikum und Metal-Gate die Parameter des IMOS bereits vor der Integration von Silizium-Germanium-Schichten verbessert. Damit wird der IMOS als tragfähiges Konzept vorgestellt, welches das Potential hat, die Gültigkeit von Moore's Law über den lateralen MOSFET hinaus zu sichern.

# 1. Theoretische Betrachtungen

Um das vertikale Stoßionisationstransistorkonzept (Impact-Ionisation-MOSFET, IMOS) theoretisch erfassen zu können, erfolgt eine getrennte Betrachtung der Triangular Barriere Diode (TBD), des Kernstücks des IMOS-Transistors, und des Einflusses der Gateelektrode. Vorgestellt werden die bis zu diesem Zeitpunkt veröffentlichten theoretischen Ergebnisse und die Anwendung der Theorien auf die in dieser Arbeit vorgestellten Bauteile. Zusätzlich wird der aktuelle Stand der Technik des IMOS behandelt und die bisher existierenden Konzepte vorgestellt.

Die Unterschiede in Aufbau und Funktion zwischen lateralem MOSFET, vertikalem MOSFET, lateralem IMOS und vertikalem IMOS sind sehr groß. Besonders der Ladungstransportmechanismus ist physikalisch sehr verschieden. Somit kann die konventionelle MOSFET-Theorie, die in der Literatur ausführlich behandelt ist [6, 17], nur als Ausgangsbasis dienen. In diesem Kapitel wird daher eine Möglichkeit skizziert, den vertikalen IMOS-Transistor theoretisch zu beschreiben.

### 1.1. Triangular Barrier Diode

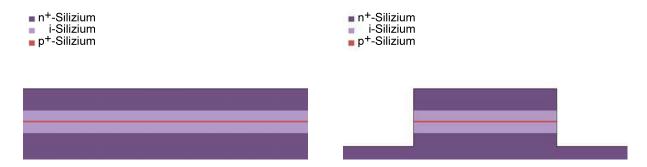

Abb. 1.1.: Schnitt durch epitaktische Schichtstapel und freigestellte Mesastruktur mit Delta-Dotierung

Die TBD bildet das Kernstück des hier behandelten vertikalen Stoßionisationstransistorkonzeptes. Es handelt sich um eine Weiterentwicklung der von Shannon behandelten Camel-Diode [18], deren Stromdichte auf der Kontrolle der Höhe einer Potentialbarriere basiert. Zwischen zwei dotierten Gebieten, die die Elektroden bilden, ist eine undotierte Schicht der Länge  $L_i = L_1 + L_2$  eingebettet. In dieser befindet sich eine den Elektroden

entgegengesetzt dotierte Schicht. Abbildung 1.1 zeigt den Schichtstapel (links) und eine isolierte Mesastruktur (rechts), wie sie für die TBD erforderlich ist. Die Schicht, die die Barriere bildet, ist so dünn, dass sie auch ohne angelegte Spannung vollkommen an freien Ladungsträgern verarmt ist. Bei der TBD ist wird diese Schicht als infinitesimal dünn angenommen und wird deswegen nach der entsprechenden mathematischen Funktion auch als Delta-Schicht bezeichnet (Abbildung 1.2a und b). In der Realität beträgt die Dicke wenige Nanometer.

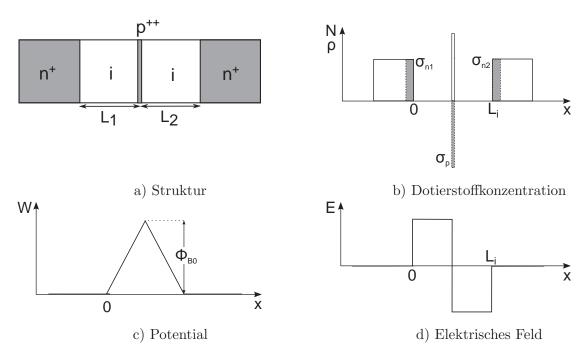

Abb. 1.2.: Struktur, Feld, Potentialverlauf und Dotierstoffkonzentration in einer TBD

Im Folgenden wird von einer vollkommen verarmten Delta-Schicht ausgegangen, so dass diese als negative Flächenladung der Ladungsdichte  $\sigma_p = qNd(\delta)$  mit der Elementarladung q, der Dotierstoffkonzentration N und der Breite der Delta-Schicht  $d(\delta)$  angenommen wird (Abbildung 1.2b). Die Lösung der Poisson-Gleichung ergibt den namensgebenden dreieckförmigen Verlauf des elektrischen Potentials. Die Höhe der Dreiecksbarriere wird mit  $\phi_{B0}$  bezeichnet (Abbildung 1.2c), die Breite der Basis des Dreieckskann näherungsweise als  $L_i = L_1 + L_2$  angenommen werden. Das elektrische Feld in den intrinsischen Schichten ist konstant (Abbildung 1.2d).

### Funktionsweise und Modellierung

Elektrisch entspricht die TBD zwei gegenläufig geschalteten pin-Dioden, wobei die mittlere Elektrode, von der Delta-Schicht gebildet, nicht kontaktiert ist. Eine dotierte Schicht ist geerdet, an die andere wird eine Spannung V angelegt. Je nach Vorzeichen der Span-

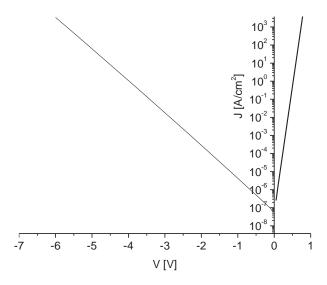

nung ist damit eine der Dioden in Sperr- und die andere in Durchlassrichtung gepolt. Die Kennlinie zeigt bei niedrigen negativen und positiven Spannungen einen für pin-Dioden üblichen Sperrbereich. Bei Erhöhung der Spannung erfolgt ein abrupter Durchbruch. Die ideale elektrische Kennlinie einer symmetrischen TBD ist in der logarithmischen Auftragung des Betrags des Stromes achsensymmetrisch. Die Symmetrie ist abhängig von dem Verhältnis der i-Zonen-Längen und den Dotierungen der Kontaktgebiete.

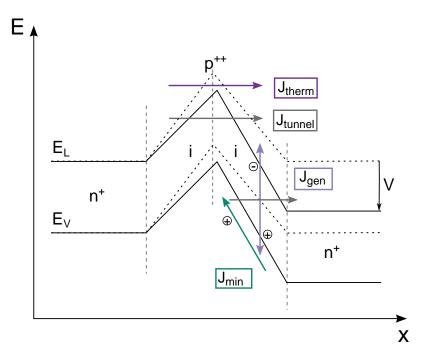

Abb. 1.3.: Stromtransportmechanismen in einer TBD

Für p-dotierte Delta-Schichten ergibt sich die in Abbildung 1.3 gezeigte Bandstruktur. Die gestrichelten Linien zeigen die Bänder ohne angelegte Spannung, die durchgezogenen Linien stellen die Bandstruktur mit einer an einer Elektrode liegenden positiven Spannung dar wenn die andere Elektrode geerdet ist. Mit zunehmender Spannung verringert sich die Barrierehöhe und Stromfluss setzt ein, sobald die Barriere von Ladungsträgern überwunden werden kann. Im Unterschwellbereich vor dem Durchbruch müssen vier Stromtransportmechanismen nach Abbildung 1.3 in Betracht gezogen werden:

- Thermische Emission über die Barriere

- Strom aus in den intrinsischen Gebieten erzeugten Minoritätsladungsträgern

- Generations-/Rekombinationsstrom

- Tunnelstrom durch die Barriere

#### Thermischer Emissionsstrom

Signifikanter Stromfluss setzt ein, wenn die Barriere soweit gesenkt ist, dass sie von thermischen Elektronen überwunden werden kann. Als dominierender Stromtransportmechanismus wird in der TBD analog zur Schottkybarriere thermische Emission über die Barriere angenommen [6]. Die Höhe der Barriere hängt von der Dotierung und Dicke der Delta-Schicht, der Länge der umgebenden intrinsischen Zonen und der Dotierung der Kontaktgebiete ab und beträgt üblicherweise etwa 1eV. Für die thermische Emission ist nur die Höhe, nicht die Form der Barriere von Bedeutung. Zur Berechnung der Barrierehöhe wird eine Struktur mit abrupten Dotierübergängen angenommen. Mit den weiteren Näherungen

- 1. Hintergrunddotierung der intrinsischen Zonen vernachlässigbar

- 2. Delta-Schicht völlig an freien Ladungsträgern verarmt

- 3. Potentialabfall in den dotierten n- und p-Regionen vernachlässigbar gegenüber dem Abfall in den nominell undotierten Zonen.

kann die Barrierehöhe ohne anliegende Spannung  $\phi_{B0}$  geometrisch als Lösung der Laplace-Gleichung zu [19]

$$\phi_{\text{B0}} = \frac{(\text{L}_1 \text{L}_2)}{(\text{L}_1 + \text{L}_2)} \frac{\sigma_{\text{p}}}{\varepsilon_0 \varepsilon_{\text{Si}}} \tag{1}$$

ermittelt werden, wobei  $\sigma_p$  die Flächenladung der Delta-Schicht beschreibt und  $\varepsilon$  die jeweilige Permittivität,  $\phi_{B0}$  die Barrierehöhe und  $\sigma_p$  die Flächenladungsdichte. Die Längen  $L_{1/2}$  können aus Abbildung 1.2 entnommen werden. Der resultierende Stromfluss als thermische Emission über die Barriere ergibt sich als [19, 6]

$$J_{\text{therm}} = AT^2 e^{-\frac{q\phi_{B0}}{kT}} \left( e^{\frac{qV}{kT} \frac{L_2}{L_1 + L_2}} - e^{-\frac{qV}{kT} \frac{L_1}{L_1 + L_2}} \right). \tag{2}$$

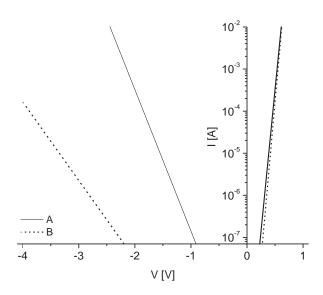

A bezeichnet die Richardson-Konstante, V die anliegende Spannung, k die Boltzmannkonstante, T die Temperatur und q die Elementarladung. Die exponentielle Abhängigkeit des Stroms von der Barrierehöhe resultiert in großen Auswirkungen auf den Strom bereits bei geringfügigen, unvermeidbaren Abweichungen der ermittelten Barrierehöhe. Abweichungen zu den experimentellen Ergebnissen zeigen sich besonders im Übergang zu höheren Stromdichten im Unterschwellbereich. Sie resultieren aus der Annahme der Ladungsverteilungen als Flächenladungen. In halblogarithmischer Darstellung entspricht Gleichung 2 einer Geraden, wie in Abbildung 1.4 oben für zwei verschiedene Gallium-Arsenid-Dioden gezeigt ist. Diode A hat i-Zonen-Längen von 50 und 200nm und eine Flächendotierung von  $1 \cdot 10^{12} \text{cm}^{-2}$ , Diode B i-Zonen-Längen von 25 und 200nm und eine Flächendotierung von  $2 \cdot 10^{12} \text{cm}^{-2}$ .

Wird die Diffusion mobiler Ladungsträger aus den dotierten Gebieten x < 0 und  $x > L_1 + L_2$  in die i-Zonen berücksichtigt, ergibt sich die Barrierehöhe  $\phi_z$  von der linken (z=1)

Abb. 1.4.: Modellierung des thermischen Emissionsstroms in einer TBD nach [19] (oben) und [20] (unten)

beziehungsweise rechten (z=2) Seite der Barriere unter der Bedingung eines hinreichend hohen Feldes in der intrinsischen Zone  $E_{L1} > \sqrt{4kTN_d/\varepsilon}$  zu [20]

$$\phi_{z} = -|E_{z}|L_{z} + \frac{kT}{q}\ln\left\{\frac{2E_{z}}{E_{0}}\left[1 + \left(\frac{E_{z}}{E_{0}}\right)^{2}e^{1 + (E_{z}/E_{0})^{2}}\right]^{1/2} - \left[\left(\frac{E_{z}}{E_{0}}\right)^{2}e^{1 + (E_{z}/E_{0})^{2}}\right]^{1/2}\right\}^{2}$$

(3)

mit z=1 oder 2 für die linke oder rechte Seite der Barriere,  $E_0 = \sqrt{kTN_d/\varepsilon}$ , bei einer Dotierung von  $10^{18} \rm cm^{-3}$  etwa  $60 \rm kV/cm$ ,  $\phi_z$  die Barrierehöhe auf der jeweiligen Seite der Barriere,  $\phi_1 - \phi_2 = V$  und  $E_1 - E_2 = \frac{\sigma_p}{\varepsilon_0 \varepsilon_{\rm Si}}$  als von der Flächenladung  $\sigma_p$  verursachter Sprung im elektrischen Feld. Damit folgt der thermische Emissionsstrom als [20]

$$J_{therm} = A \cdot T^2 \left(e^{\frac{q\phi_1}{kT}} - e^{\frac{q\phi_1 - V}{kT}}\right). \tag{4}$$

Für Diode B ist die Kennlinie in Abbildung 1.4 unten gezeigt.

Die TBD wird hierbei als unipolares Bauteil betrachtet. Diese Annahme ist gerechtfertigt, wenn die Delta-Schicht bei völliger Verarmung als Flächenladung angenähert wird. Damit dominiert die Injektion von Majoritätsladungsträgern und der Strom wird alleine von diesen getragen. Mit diesen Voraussetzungen liefern die Modelle eine gute Näherung für TBDs, deren Barrierehöhe kleiner ist als die Hälfte der Bandlücke Eg [21].

#### Minoritätsladungsträgerstrom

Für hohe Dotierungen bis hin zu einer Konzentration freier Löcher nahe der Konzentration ionisierter Akzeptoren und damit hohe Barrieren haben Minoritätsladungsträger einen deutlichen Einfluss auf die elektrischen Eigenschaften [22].

Sobald die Delta-Schicht nicht mehr vollkommen an freien Ladungsträgern verarmt ist, wird bei Anlegen einer Spannung zuerst die Ladung in der Delta-Schicht kompensiert. Währenddessen bleibt die Barrierehöhe annähernd konstant. Erst nachdem die Delta-Schicht an freien Ladungsträgern verarmt ist, setzt der Einfluss der Spannung auf die Barrierehöhe und damit Stromfluss durch thermische Emission über die Barriere ein. Im hier betrachteten Fall mit n-dotierten Elektrodengebieten sind die Minoritätsladungsträger Löcher und die Majoritätsladungsträger Elektronen. Soll der Einfluss der Minoritätsladungsträger auf die Barrierehöhe analytisch erfasst werden, wird von der Poisson-Gleichung der Form

$$\frac{\mathrm{dE}}{\mathrm{dx}} = \frac{\mathrm{q}}{\varepsilon_{\mathrm{Si}}} (\mathrm{p} - \mathrm{n}) \tag{5}$$

ausgegangen mit p und n als Anzahl der jeweiligen freien Ladungsträger [23]. Damit kann bei Annahme des Gleichgewichtszustandes für Löcher pE  $=\frac{kT}{q}\frac{dn}{dx}$  und analog für Elektronen unter Vernachlässigung der Löcherkonzentration um x=0 das elektrische Feld nahe der Elektrode E<sub>1</sub> und in der Nähe der Delta-Schicht unter Vernachlässigung